Introduction to Verilog

Verilog is an HDL (Hardware Description Language) used to write an RTL code for a hardware design. To design any hardware, we first need to draw the schematics using Boolean equations and making schematics can be tiresome and prone to human errors. To tackle this problem, HDLs were introduced. We can model the hardware design in different levels of abstraction, and the program will convert that code into schematics representing actual gates and nets.

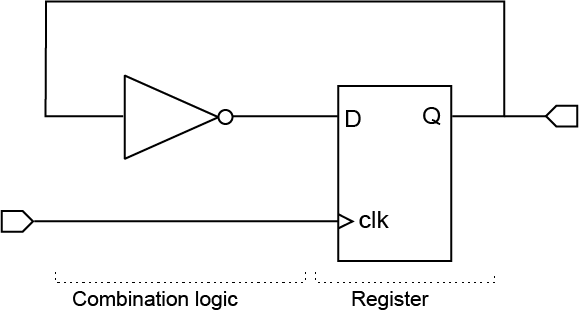

Most of the newcomers will not be aware of what RTL means. RTL stands for Register Transfer Logic. RTL is a level of abstraction in which most of the hardware is designed in the present time. We model hardware in terms of the flow of digital signals, i.e., data, between hardware registers (basically a D flip-flop). All the logical operations are performed on these signals.

Brief History

Verilog was introduced in 1985 by a group of engineers and scientists. It was made open standard for HDL in late 1995.

Verilog was standardised as IEEE 1364 when it was made open standard, and later it was merged with System Verilog and standardised as IEEE 1800. The current version of Verilog is IEEE 1800-2017.

Verilog vs VHDL

2 HDLs are very common in the market:

- Verilog

- VHDL (Very High-Speed Integrated Circuit HDL)

Verilog is nowadays more popular than VHDL as hardware can be more accurately modelled in Verilog than in VHDL.

Understanding the difference between the two languages makes it easier to choose the correct language for a project as both has its advantage. Also, for freshers, this is a common interview question in any VLSI company.

| Verilog | VHDL |

|---|---|

| Verilog is a weakly typed language. Weakly typed language means that the data type can be implicitly converted by the compiler, if possible, without throwing an error. | VHDL, on the other hand, is a strongly typed language. In a strongly typed language, the compiler will throw an error in case of a data type mismatch. |

| Verilog has low verbosity. Verbosity, in general, means the number of words used to express something. Thus in Verilog, the amount of code that needs to be written is less. | VHDL has high verbosity. Thus, more codes need to be written. |

| Verilog is case sensitive. | VHDL is not case sensitive. |

| Verilog is based on the C language, and thus it is easy to learn. | VHDL is based on ADA and PASCAL, and thus it may be challenging to learn as most people are familiar with the C language. |

| Verilog represents hardware more accurately. | VHDL represent hardware less accurately. |

Some of the terms like Verbosity and Weakly typed language may be new for many readers, and thus, it is recommended to study more about them.

Need for HDLs

Most of us would have learnt about Boolean algebras, Truth tables, K-Maps, and other concepts. Also, we would have used these techniques to make a schematic for various digital designs like an adder, subtractor, and other basic circuits.

So, what is the need for HDL, then? Why do we need to learn to code in Verilog or VHDL before designing something that can be used in real life?

In colleges, we would have made schematics manually by writing the truth table and reducing it using K-Maps or Boolean algebras, but the designs are complex in real life. There are thousands and thousands of gates, even in a simple design. This fact makes the designing of digital circuits manually a tough job.

HDL comes to help in this situation. These languages provide us with a way to design a complex problem statement by breaking it into small modules. The codes which we write in HDL is synthesised into schematic automatically during the synthesis process. Synthesis means converting the RTL code into the gate-level schematic, which can be further made into a chip. This process removes the chances of any human error which might have been introduced if it had been done manually.

There is also the advantage of mixed modelling in HDL. For example, let us suppose we have to design an 8-bit ALU (Arithmetic Logic Unit). We know in ALU there can be various operations like addition, subtraction, comparison, etc. At a time, the ALU would be performing only one operation, and thus, ALU must have a decoder circuit in it. If we make the schematic manually, we must make the entire decoder by writing the truth table, K-Map, which would make the process tiresome.

However, in HDL, we can use the simple switch-case statements for different operations, and the decoder circuit will be made automatically during the synthesis process. Thus, we could focus more on designing the circuit for individual operations. Please note, it is referred to as mixed modelling because not every statement is directly synthesisable. Thus, we will have to make a Boolean equation for the addition and other arithmetic operations before writing it in HDL.

We hope now it will be easy to realise the need for HDL and why we need to learn to write code in Verilog or VHDL despite knowing the digital concepts.